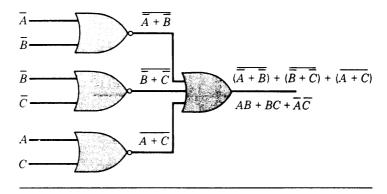

NOR-to-NOR gate network analysis.

# **NAND-TO-AND AND NOR-TO-OR GATE NETWORKS**

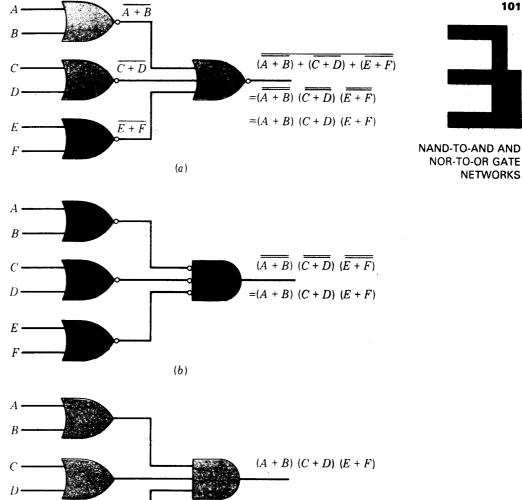

3.23 In the two preceding sections, we showed how to analyze and design networks using NAND and NOR gates in NAND-to-NAND and NOR-to-NOR forms. Two other forms are in common usage: the NAND-to-AND and the NORto-OR forms.

(c)

Since NAND gates are quite popular and since the outputs from NAND gates

NOR gate network analysis.

> sometimes can be ANDed by a simple connection, as we show later, we first present the analysis and design procedures for NAND-to-AND gate networks.

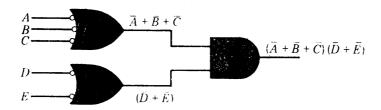

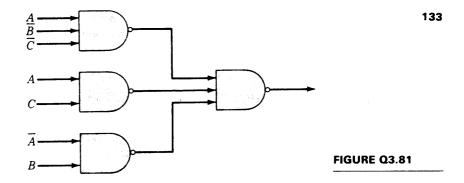

> Figure 3.33(a) shows a NAND-to-AND gate network with inputs A, B, C, D, and E. Figure 3.33(b) shows the same configuration but with the NAND gates replaced by the equivalent NAND gate symbol from Fig. 3.24. This shows a NAND-to-AND network functions like an OR-to-AND network with each input complemented and leads to this design rule.

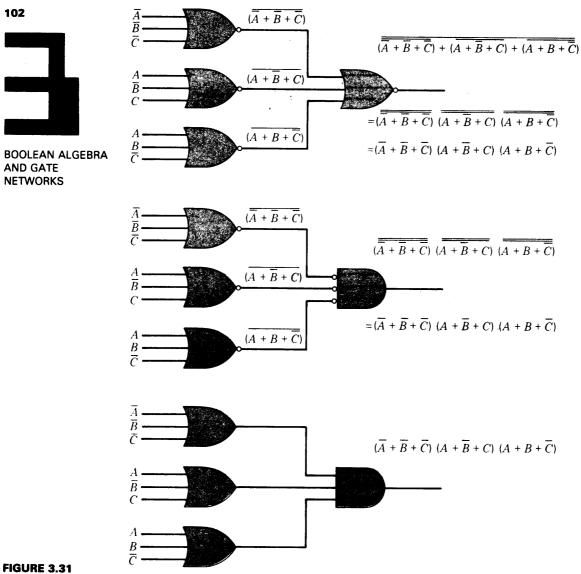

Two NOR gate designs.

a. Conventional NAND to AND gate network

#### FIGURE 3.33

NAND-to-AND gate network. (a) Conventional NAND-to-AND gate network. (b) NAND-to-AND with equivalent gates substituted.

b. NAND-to-AND in (a) but with equivalent gates substituted for NANDs.

# **DESIGN RULE**

# Example

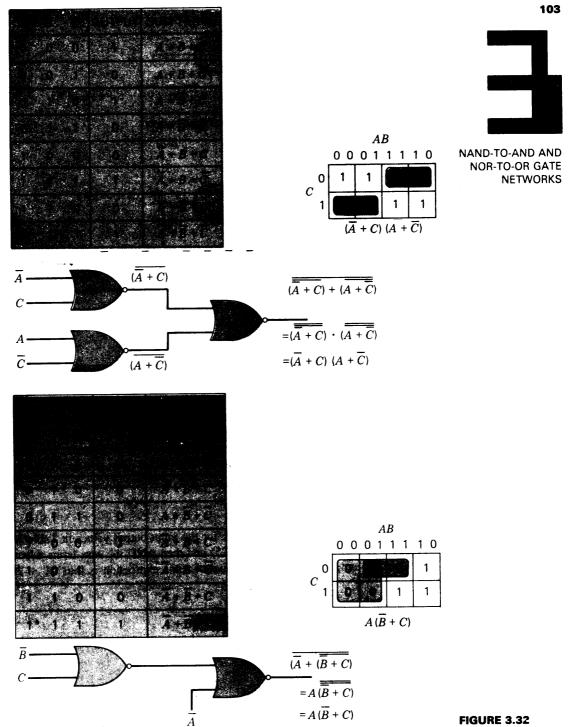

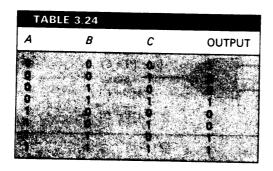

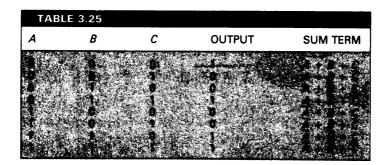

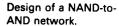

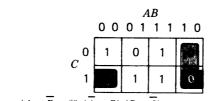

Design a NAND-to-AND gate network for the input-output values in Table 3.24. We add a sum-term column (Table 3.25) and then AND the sum terms where 0s appear in the output values. Our product-of-sums expression is thus (A + B + B)

NAND-TO-AND AND NOR-TO-OR GATE NETWORKS

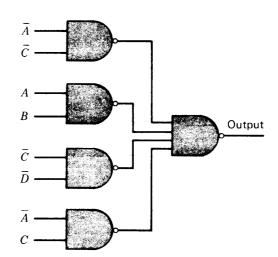

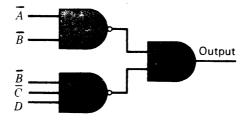

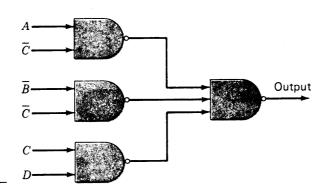

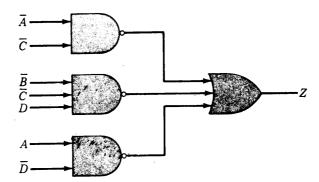

$\overline{C}$ )( $A + \overline{B} + C$ )( $\overline{A} + B + C$ )( $\overline{A} + B + \overline{C}$ ). This must be simplified. The simplified expression is  $(A + \overline{B} + C)(\overline{A} + B)(B + \overline{C})$ . The rule states that we must now form a NAND-to-AND gate network, but that each input should be complemented. This means each variable in  $(A + \overline{B} + C)(\overline{A} + B)(B + \overline{C})$  must be complemented. The inputs for one NAND gate thus will be  $\overline{A}$ ,  $\overline{B}$ , and  $\overline{C}$  which are from the first sum term  $(A + \overline{B} + C)$ . The inputs to the second NAND gate will be  $\overline{A}$  and  $\overline{B}$  from the term  $\overline{A} + B$ , and the third NAND gate will have as inputs  $\overline{B}$  and  $\overline{C}$  from the sum term  $(B + \overline{C})$ . The resulting block diagram is seen in Fig. 3.34.

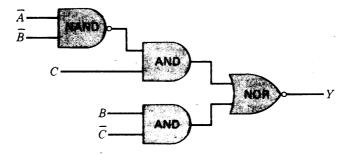

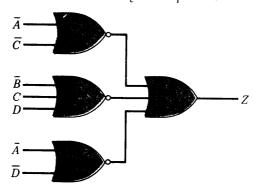

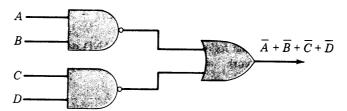

NOR-to-OR gate networks are also widely used because NORs are the natural gates for emitter-coupled logic (ECL) circuits, a major circuit line. Figure 3.35(a) shows a NOR-to-OR gate network with four inputs and the output boolean algebra expressions. Figure 3.35(b) shows the same configuration but with equivalent gates from Fig. 3.29 substituted for the NOR gates. This shows that the basic form for the boolean expression realized is AND-to-OR but with each input variable complemented. Thus the design rule for a NOR-to-OR gate network is as follows:

$(A + \overline{B} + C) (\overline{A} + B) (B + \overline{C})$  is simplified expression

BOOLEAN ALGEBRA AND GATE NETWORKS

# Above net with equivalent gates from Fig. 3.29 substituted for NOR gates

$\frac{(\overline{A} + \overline{B}) + (\overline{C} + \overline{D})}{\overline{A} \cdot \overline{B} + \overline{C} \cdot \overline{D}}$

$\overline{A+B}$

#### FIGURE 3.35

NOR-to-OR gate network and equivalent network.

#### **DESIGN RULE**

A design a NOR to OR gate network, develop and simplify the same of products expression for the described function. Then draw a NESS-to-OR gate network with a NOR gate for each product term, but samplement each input in the sum-of-products expression to form the input to the NOR gates.

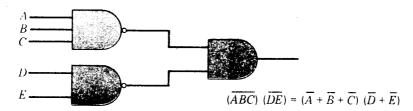

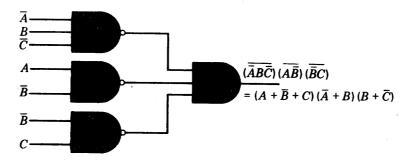

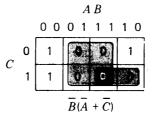

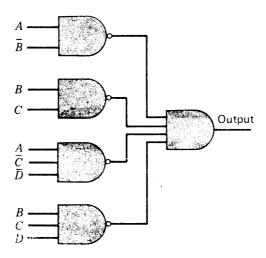

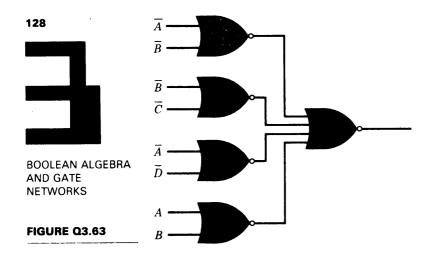

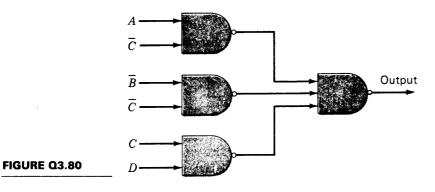

Table 3.26 shows a table of combinations to be realized as a NOR-to-OR gate network. The product terms are added to the table, and then the boolean algebra expression is derived for the problem:  $\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$ . This expression is then simplified, giving  $AB + BC + \overline{AC}$ .

The design rule says that to realize a NOR-to-OR gate network we use the above expression but complement each input. This means the first NOR gate will

Design for NOR-to-OR gate network.

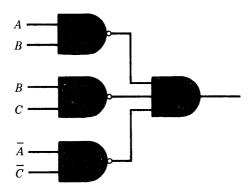

have as inputs  $\overline{A}$  and  $\overline{B}$  from the product term AB; the second NOR gate will have as inputs  $\overline{B}$  and  $\overline{C}$  from the product term BC; and the third NOR gate will have as inputs A and C from the product term  $\overline{AC}$ . Figure 3-36 shows this design.

#### **WIRED OR AND WIRED AND GATES**

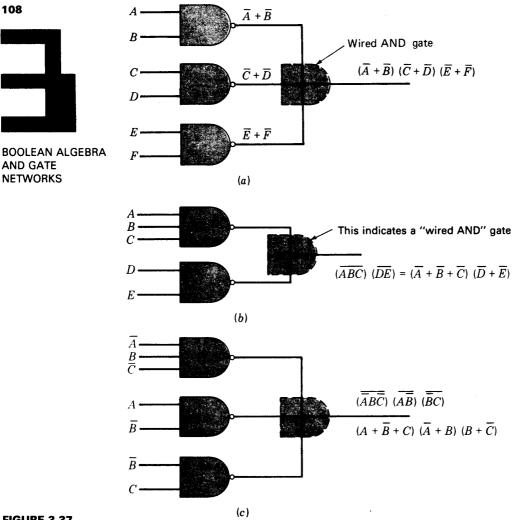

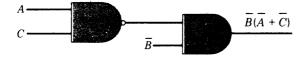

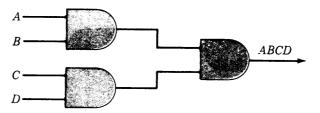

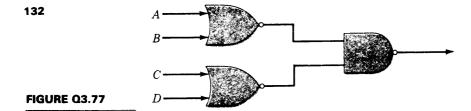

\*3.24 In certain integrated-circuit technologies, it is possible to form OR and AND gates by means of a simple connection. Figure 3.37(a) shows a NAND-to-AND gate combination in which the AND gate is formed by simply connecting the NAND gate outputs. The wired AND gate in Fig. 3.37(a) requires no additional circuitry beyond that required for the NAND gates. This is shown by the dotted lines used in the NAND symbol.

Only certain NAND gates can have their outputs connected in this way and still form an AND gate. The designer of the NAND gates arranges for this feature, and the manufacturer will indicate on the specification sheet when this can be done. For example, when transistor-transistor logic (TTL) circuits are used, the specification sheets sometimes refer to the gates as having "open collectors," which means they can be formed into NAND-to-AND nets by simply connecting their outputs. In effect, the circuits are designed so that the output level of all gates when the gates are connected will be the lowest level any gate would output if the gates were operated singly.

Figure 3.37(b) and (c) shows examples of NAND-to-wired-AND nets which correspond in function to those in Figs. 3.33 and 3.34. Again, we emphasize that not all NAND gates can be wire-ANDed by using a simple connection. When this is possible, however, the saving in circuitry and speed improvement makes the configuration desirable.

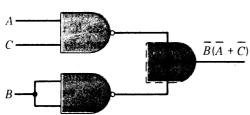

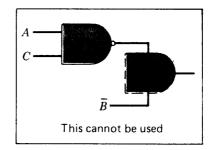

An important observation should be made here: If inputs are wire-ANDed by using a simple connection, a single variable cannot be tied to the AND connection. A single input NAND gate (inverter) must be used. Refer to Fig. 3.38, which shows a design where a single variable B occurs in the minimal expression.

To explain this problem, if in Fig. 3.38 A and C are each 1 and B is 0, then the NAND gate output should be 0, while the value of  $\overline{B}$  is 1. What would the value at the wired AND junction be? Will the NAND gate output pull  $\overline{B}$  down, or

NAND to wired AND networks. (a) NANDto-AND with wired AND gate. (b) NANDto-AND with wired AND for Fig. 3.33(a). (c) NAND to wired AND for Fig. 3.34.

will the 1 on  $\overline{B}$  force the level up? The situation is to use an AND gate, not a wired AND, or to use a NAND gate with the ability to have its output wire-ANDed, as shown in Fig. 3.38.

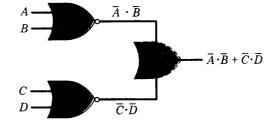

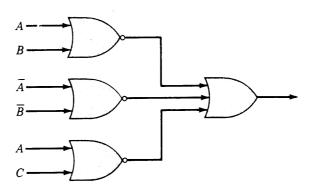

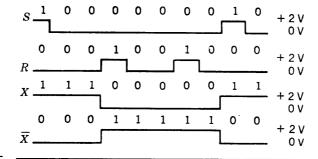

Some NOR gates will form an OR gate at their output when they are connected. Figure 3.39 shows a NOR-to-wired-OR net with output function  $(\overline{A} + \overline{B}) + (\overline{C} + \overline{D}) = \overline{A} \cdot \overline{B} + \overline{C} \cdot \overline{D}$ . This expression,  $\overline{A} \cdot \overline{B} + \overline{C} \cdot \overline{D}$ , shows us that the NOR-to-OR gate network functions as an AND-to-OR gate network but with each variable complemented. Again, the dotted symbol shows the gate is wired OR.

The above result shows that we can design for NOR-to-wired-OR networks just as for NOR-to-OR networks.

Again, note that only certain NOR gates can be connected at their outputs to

NAND-to-AND gate design with single variable.

form wired ORs. Some ECL circuits make this possible, and the manufacturer notes this on the specification sheets.

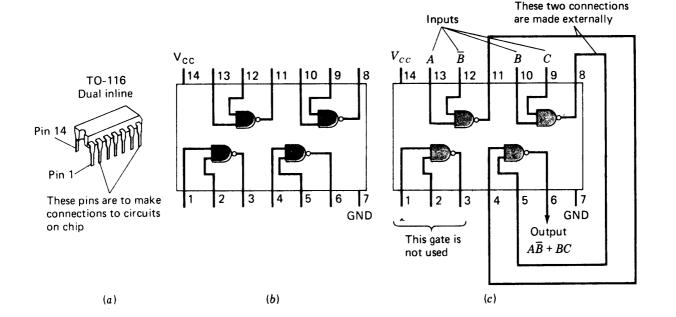

#### **PLAs AND PALs**

\*3.25 When a design has been made for a gate network, the next step is to implement the design using integrated circuits. As has been mentioned, the most used IC line for gate networks has been a line called transistor-transistor-logic (TTL). Figure 3.40(a) shows an IC container, and Fig. 3.40(b) shows the gate layout in that container. This is called the pin-out for the IC package. The package in Fig. 3.40(b) is one of several hundred different gate layouts from which a designer can choose. By using this particular IC package, the NAND-to-NAND gate network for  $A\overline{B} + BC$  can be realized by connecting the pins of the package as shown in Fig. 3.40(c). These connections are often made as conducting metallic strips on printed-circuit boards on which the IC containers are mounted.

NOR-to-wired-OR gate network.

As the number of gates in a network increases, more IC packages such as that in Fig. 3.40 are required. To decrease the number of IC packages required and simplify interconnecting the packages, IC manufacturers have evolved manufacturing processes which greatly increase the number of gates that can be placed in a single IC container. This large-scale integration leads to several basic design problems, however. For example, the inputs and outputs to the gates in Fig. 3.40 are all available and the gates can be interconnected in any desired manner, but if more gates are placed in a single container, the number of pins in the IC container must be increased. This increases the cost of the container substantially and decreases the ability of the designer to select just the right combination of gates for the network. Also connections must still be made outside the IC container. If the same connections are made inside the container (on the IC chip), they would cost less and be more reliable. This leads to the idea of a chip with a specific gate layout made for a particular design is called a *custom* chip. Unfortunately,

# FIGURE 3.40

Integrated-circuit container and pin-out.

(a) Integrated circuit container. (b) Pin-out showing gate layout in container in (a). (c) NAND-to-NAND gate set realizing  $A\overline{B} + BC$ .

generating a complete design for a new individual custom IC chip<sup>12</sup> can be very expensive (costs can be from \$50 to several hundreds of thousands of dollars). This means that start-up costs for a computer design that requires a number of custom chips can be very high. Once custom chips are made, however, for large runs, the cost per manufactured chip is low.

The high start-up costs for custom chips have caused designers to use IC packages with only a few gates per package, as in Fig. 3.40, and form the gate networks by interconnecting the gates outside the IC packages (using a printed-circuit board, as previously noted), particularly when small numbers of the design are to be made. However, although this approach is practical and economical for small production runs, it does not utilize the level of integration<sup>13</sup> possible for present ICs.

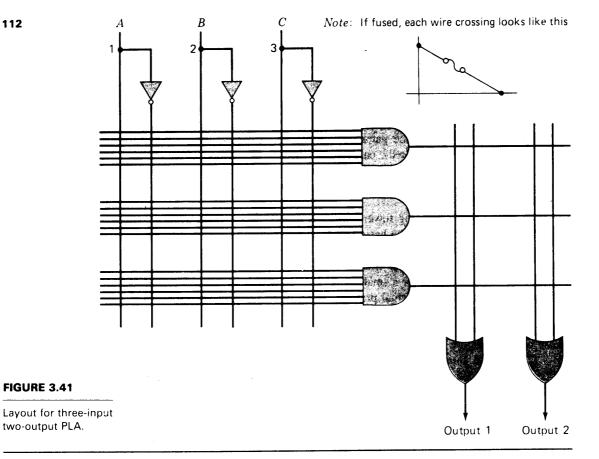

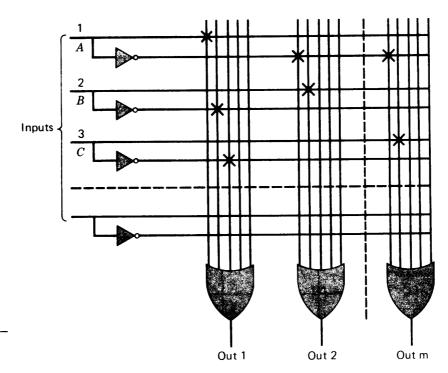

To aid designers in using fewer chips, IC manufacturers make *semicustom* chips in IC containers in which a basic two-level gate network with many gates is produced and the gates can be interconnected on the chip as desired. These are called *programmable logic arrays* (PLAs) or *programmable array logic* (PALs). <sup>14</sup> Figure 3.41 shows a layout for a small PLA. This particular array has three AND gates and two OR gates. (In actual practice, an array would have several hundred or more gates.) Note that the connections from inputs A, B, C, to the AND gates are not complete and that the AND gate outputs are not connected to the OR gates. These connections are made as desired by the gate network designer.

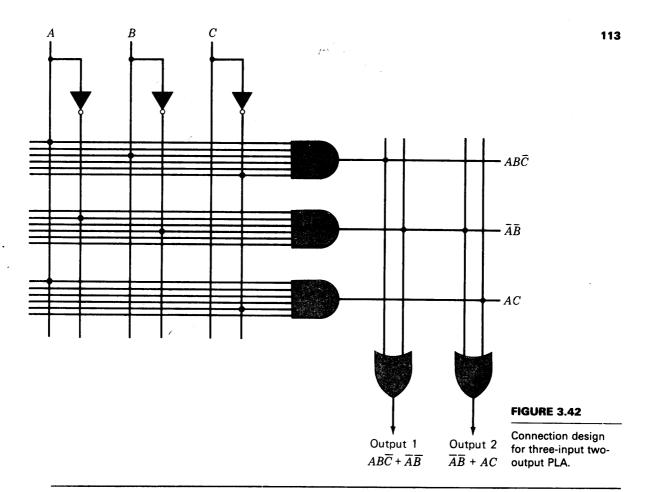

Figure 3.42 shows a design which uses the PLA in Fig. 3.41 and which realizes the two boolean algebra expressions  $AB\overline{C} + \overline{AB}$  (for output 1) and  $\overline{AB} + AC$  (for output 2).

These PLAs are manufactured in two different ways. In the first, the manufacturer places a fused connection at every intersection point in the PLA between the inputs and the AND gates and between the AND and OR gates. Thus every possible connection is made when the PLA is manufactured, and then the undesired connections are removed by blowing the fuses. <sup>15</sup> This type of PLA is often called a *field-programmable logic array* (FPLA).

In the second manufacturing technique, the desired connections are made during manufacture. The manufacturer originally makes the IC array layout so that any desired connections can be made, and the logic designer tells the manufacturer which connections to make for a particular design. Then the manufacturer creates a *mask*, which generates the desired connections when layers of metallization are added to the chip during manufacture. Setting up this mask costs far less (several hundred dollars or less) than designing an entire new chip with the precise logic

PLAs AND PALS

<sup>&</sup>lt;sup>12</sup>A custom IC chip is one made from scratch for a particular purpose. A particular gate configuration can be manufactured into a chip by developing the masks used to produce the chip design.

<sup>&</sup>lt;sup>13</sup>The level of integration is the complexity of the chip in terms of gates per chip. *Small-scale integration* (SSI) is roughly 1 to 20 gates per chip, *medium-scale integration* (MSI) is 20 to 100 gates per chip, *large-scale integration* (LSI) is 100 to 1000 gates per chip, and *very large-scale integration* (VLSI) is more than 1000 gates.

<sup>&</sup>lt;sup>14</sup>PAL is a registered trademark of Monolithic Memories.

<sup>&</sup>lt;sup>15</sup>The fuses are blown by selecting a fuse using logic levels at the inputs and then applying a relatively high voltage to a pin on the IC container. Electronic instruments can be purchased which blow selected fuses on a PLA. This is called *programming* the PLA.

array desired by the logic designer. And production runs of these chips are inexpensive.

Note that the AND gate which generates  $\overline{AB}$  in Fig. 3.42 has its output connected to two OR gates. This is sometimes a useful and desirable feature for PLAs enabling a single AND gate to be used for two outputs.

Most larger PLAs contain several hundred gates, 15 to 25 inputs, and 5 to 15 outputs. This offers the logic designer great flexibility. The low cost per unit of these IC gate networks has led to widespread use of PLAs.

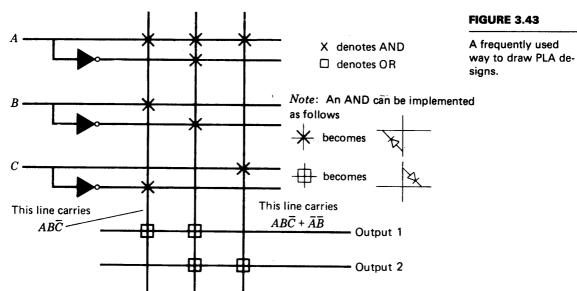

To design these large arrays, a simplifying symbology has proved useful. Figure 3.43 shows this for the array in Fig. 3.42. The crosses drawn on the function indicate ANDs, and the squares indicate ORs. The figure also shows that the AND can be realized by a single semiconductor junction (called a diode), and the OR can be realized by a single junction pointed the other way. In practice, the manufacturer lays out the chip with junctions at every intersection of the lines, and only the desired diode connections are made. 16 Note: This is simply a redrawing of Fig.

<sup>&</sup>lt;sup>16</sup>For field-programmable logic arrays (FPLAs) the diodes are fused so they can be blown by an instrument called an array programmer. This sets the FPLA as desired.

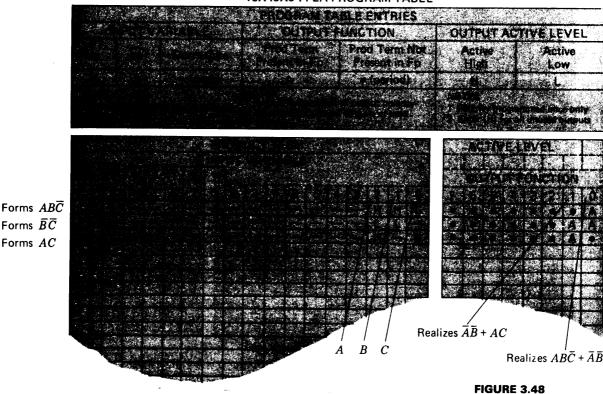

PAL design for  $\overrightarrow{ABC}$ +  $\overrightarrow{AB}$  +  $\overrightarrow{AC}$ .

# 16X48X8 FPLA PROGRAM TABLE

|               |                                           | 1                   |                   |                          |              |          |                |                |          |          |              |              |              |              |          | OG       | RAM            |                                                  |                 |          | ITRI           | ES                                               |          |               |              |                                                  |                |                                                  | <u> </u>        |              |            |

|---------------|-------------------------------------------|---------------------|-------------------|--------------------------|--------------|----------|----------------|----------------|----------|----------|--------------|--------------|--------------|--------------|----------|----------|----------------|--------------------------------------------------|-----------------|----------|----------------|--------------------------------------------------|----------|---------------|--------------|--------------------------------------------------|----------------|--------------------------------------------------|-----------------|--------------|------------|

| -             |                                           |                     |                   |                          |              |          | 11             | NPU            | T V      | ARI      | ABL          | E            |              | Ι            |          |          | JTPL           |                                                  |                 |          |                |                                                  | Т        | _             | DUT          | PUT                                              | AC             | TIV                                              | E LE            | EVF          | <br>I      |

|               | ဂ္ဂ                                       |                     |                   |                          |              | Im       |                | In             | -<br>-   | D        | on t         | Ca           | re           | ,            |          | d T      | erm<br>in Fr   |                                                  | Pr              | od.      |                | 1 No                                             | •        |               | Acti         | ve                                               | Ĭ              |                                                  | Act             | ive          |            |

|               |                                           |                     |                   |                          |              | Н        |                | L              |          | -        | – (d         | ash          | )            |              |          | A        |                |                                                  |                 |          | erio           |                                                  | -†       |               | Н            |                                                  | +              |                                                  |                 |              |            |

|               | N.                                        |                     |                   |                          |              | NO       |                |                |          |          |              |              |              |              | TES      |          |                |                                                  |                 |          |                |                                                  | 1        | N             | OTES         | 3                                                |                | _                                                |                 |              |            |

|               | THIS FORTION TO BE COMPLETED BY SIGNETICS |                     |                   |                          |              |          | er :           | for u          | nuse     | d inp    | uts o        | f use        | a            | 2            | Entri    | A &      | epend<br>pruni | sent :                                           | of out<br>cutpu | put p    | olarıt<br>used | y<br>P-tern                                      | 15       | 1 2           | Poi<br>Ent   | arity (<br>er •H                                 | orogr<br>for a | amm<br>H un                                      | ned on          | outp         | nly<br>uts |

|               | 9                                         |                     |                   |                          |              |          |                |                |          |          |              | PR           | ODI          | JCT          | TE       | 3M1      |                | _                                                |                 | =        |                |                                                  | 1        | $\overline{}$ |              | ACI                                              | IVE            | I F                                              | VFI             | ,            |            |

|               | 1                                         |                     | -                 |                          |              | NO       | - ,-           | 7              | Γ,-      | ٦-       | Γ,           |              | _            | VAF          | IIAE     | LE       |                |                                                  |                 |          |                |                                                  | 1        | ļ .           |              | I -                                              | T              | <u>-</u> ر                                       |                 |              |            |

|               |                                           | j                   |                   |                          |              |          | 5              | 4              | 3        | 2        | ,            | 0            | <u>ا</u> و   | T 8          | 17       | Гя       | 7 5            | 14                                               | T 3             | 1-2      | 7 7            | - <sub>0</sub> -                                 | 1        |               |              | JTP(<br>  5                                      | JT 1<br>1 4    |                                                  | IČTI<br>T 2     | DN.          | ¬          |

|               | 3                                         |                     |                   | 1                        |              | 0        |                |                |          |          |              |              |              |              |          |          |                | İ                                                |                 |          |                | Ť                                                | 1        | H             | Ť            | Ť                                                | -              | ╁                                                | <del>ا '</del>  | <del>†</del> | 0          |

|               | #                                         | *                   |                   |                          |              | 1 2      |                | _              |          | ⊬        | <u> </u>     | ــ           | ╄            | ↓_           | $\perp$  |          |                | Ļ                                                | oxday           | $\Box$   | I              |                                                  | 1        |               |              |                                                  |                | L                                                | 仜               |              |            |

| 5             | 2                                         | PART                |                   |                          |              | 3        |                |                | $\vdash$ | -        | ├-           | ╁            | ╁            | +-           | ╁        | ╀╌       | +              | ┼                                                | +-              | ╀        | +-             | -                                                | 1        | _             | _            |                                                  |                | L                                                |                 | $\Box$       |            |

|               | ž                                         | ۵                   | -                 |                          |              | 4        |                |                |          |          | $\vdash$     | $\vdash$     |              | $\vdash$     | $\vdash$ | +-       | +              | +                                                | ╁               | +-       | +-             | -                                                | H        |               | ├            | <del> </del>                                     | -              | ╁                                                | ₩               | ⊬            | _          |

|               |                                           | 9                   | - 1               |                          |              | 5        |                |                |          |          |              |              |              |              |          |          |                | 1                                                |                 |          | $\perp$        | _                                                |          |               | <del> </del> | <del>                                     </del> |                | <del> </del>                                     | -               | ├            | -          |

| 8             | 5                                         | 7.12                |                   |                          |              | 6 7      | Н              | $\vdash\dashv$ | <u> </u> |          | <u> </u>     | <del> </del> |              | 1_           | 1        | 1        | <del> </del>   | Ļ                                                | $\perp$         |          |                |                                                  | 1        |               |              |                                                  |                |                                                  |                 |              |            |

| 9             | 2                                         | CUSTOMER SYMBOLIZED | ١                 |                          |              | 8        |                |                |          |          | <del> </del> | _            | +            | +            | $\vdash$ | +        | +-             | +                                                | ╁               | +        | +              |                                                  |          |               | -            | $\vdash$                                         |                | μ_                                               | $\vdash$        | $\vdash$     |            |

| 7             |                                           | ≥ .                 | DATE RECEIVED     |                          |              | 9        |                |                |          |          |              |              |              |              | 1        |          | 1              | 1                                                | T               | +        | †-             | <del>                                     </del> |          |               | ╁            |                                                  |                | -                                                | ├               | ├            |            |

| 1             | - 1                                       | Œ                   | Ē                 | S.                       |              | 10       |                |                |          |          |              |              |              |              |          |          |                |                                                  |                 |          |                |                                                  |          |               |              |                                                  |                | <del>                                     </del> | ├─              | $\vdash$     | -          |

|               | ŝ                                         | Š                   | Ē                 | COMMENTS                 |              | 12       |                | $\dashv$       |          |          |              |              | -            | -            | ļ        | ┼        | _              | -                                                | ـ               | ↓_       |                |                                                  |          |               |              |                                                  |                |                                                  |                 |              |            |

| 1             | CF (XXXX)                                 | 010                 | Ä                 | ž                        |              | 13       |                |                |          |          | -            | _            | <del> </del> | -            | -        | +-       | ┼              | ╁                                                | $\vdash$        | +-       | +-             | -                                                |          |               | -            | $\vdash$                                         |                | ├-                                               | <u> </u>        |              |            |

| •             | ű,                                        | Š                   | Ā                 | ő                        |              | 14       |                |                |          |          |              |              |              | <u> </u>     | T        | t        |                | <del>                                     </del> | t               | +        | +-             | _                                                |          |               | <u> </u>     |                                                  |                | ┢                                                |                 | -            |            |

|               |                                           |                     |                   |                          |              | 15       |                |                | _        |          |              |              |              |              |          |          |                |                                                  |                 |          |                |                                                  |          |               |              |                                                  |                |                                                  | -               |              | $\vdash$   |

| 1             | 1                                         | 1                   | - 1               | - 1                      |              | 16       | -+             | -              |          | -        |              |              |              | <del> </del> | ⊢        | ├        |                | <u> </u>                                         | <u> </u>        | _        | ļ              |                                                  |          |               |              |                                                  |                |                                                  |                 |              |            |

|               | 1                                         |                     | - 1               |                          |              | 18       |                | _              | _        |          |              | _            | -            | -            | -        | -        | -              | -                                                | ┢               | -        | +-             |                                                  | -        |               | <u> </u>     | $\vdash$                                         |                | <u> </u>                                         | -               |              |            |

| 1             |                                           |                     |                   |                          |              | 19       |                |                |          |          |              |              |              |              |          |          |                |                                                  | 1-              | ╁        | ╁              |                                                  | -        |               |              |                                                  |                |                                                  |                 | -            |            |

|               | 1 1                                       |                     |                   |                          |              | 20       |                | -              |          |          |              |              |              |              |          |          |                |                                                  |                 |          |                |                                                  |          |               |              |                                                  |                |                                                  |                 | Γ            |            |

| 1             |                                           |                     | -                 |                          |              | 21       | -+             | -+             |          |          | -            |              |              | <u> </u>     | -        | ├-       | <u> </u>       |                                                  | <u> </u>        |          | L              |                                                  |          |               |              |                                                  |                |                                                  |                 |              |            |

|               |                                           |                     |                   |                          | 11           | 23       | $\neg \dagger$ | _              | -        | _        | _            |              |              | -            | -        | -        | -              | -                                                | -               |          | -              |                                                  | 1        |               | -            |                                                  |                | L                                                | $\vdash \dashv$ | <u> </u>     |            |

|               | 1 1                                       | -                   |                   | - [                      |              | 24       |                |                |          |          |              |              |              |              |          | _        |                | -                                                | $\vdash$        | _        | -              |                                                  | +        |               |              | -                                                |                | $\vdash$                                         | $\vdash$        |              | $\vdash$   |

|               |                                           |                     |                   |                          |              | 25       | -+             | _              | _        | 4        | $\Box$       |              |              |              |          |          |                |                                                  |                 |          |                |                                                  | 1        |               |              | $\neg$                                           |                | Н                                                |                 | _            |            |

| 1 1           |                                           |                     | 1                 | - 1                      | 1 1          | 26<br>27 | $\dashv$       | $\dashv$       | -        | -        |              | -            |              |              | <u> </u> | _        |                |                                                  |                 |          |                |                                                  |          |               |              | $\Box$                                           |                |                                                  |                 |              |            |

| 1 1           |                                           |                     |                   | -                        |              | 28       | _              | $\dashv$       | +        | +        | -            | -            |              | -            |          |          |                |                                                  |                 | -        | $\vdash$       |                                                  | -        |               | _            | $\dashv$                                         |                | Щ                                                |                 |              |            |

| 1 1           |                                           |                     |                   | -                        |              | 29       |                | ユ              |          | コ        |              |              |              |              |          | -        | Н              |                                                  | <u> </u>        | -        | Н              | ᅥ                                                | H        | $\dashv$      | $\dashv$     | $\dashv$                                         |                | Н                                                |                 | $\dashv$     | -          |

|               |                                           |                     |                   | - [                      | 1 -          | 30       | -              | $\downarrow$   | -        | _        | _            |              |              |              |          |          |                |                                                  |                 |          |                |                                                  | T        |               |              | $\dashv$                                         |                | $\vdash$                                         |                 | -            |            |

| 1 1           | - 1                                       | ı                   | 1                 | ļ                        | 1 1          | 31       | $\dashv$       | -              | $\dashv$ | +        | -            | -            |              |              |          |          |                |                                                  |                 |          |                |                                                  |          |               |              | I                                                |                |                                                  |                 |              |            |

|               |                                           |                     |                   |                          |              | 33       | $\top$         | +              | +        | $\dashv$ | -            | -            |              | _            |          |          |                |                                                  | _               |          | $\vdash$       |                                                  | L        |               |              | $\dashv$                                         |                | _                                                | _               |              | $\dashv$   |

| 1             |                                           | 1                   |                   | 1                        |              | 34       |                | $\Box$         |          |          |              | 7            |              |              |          |          |                |                                                  |                 | -        |                |                                                  | ŀ        | -             | -            | -                                                | $\dashv$       | -                                                |                 |              | $\dashv$   |

| ]             |                                           |                     | 1                 |                          | 1 }          | 35       | -              | 4              | 1        | $\perp$  | [            | $\Box$       |              |              |          |          |                |                                                  |                 |          |                |                                                  |          |               |              | _                                                | $\neg$         |                                                  | -               | -+           | 1          |

|               | 1                                         |                     | ARTS              | 1                        | 1 +          | 36       | +              | +              | $\dashv$ | +        | -+           |              |              |              | $\dashv$ |          |                | $\Box$                                           |                 |          | $\Box$         | $\Box$                                           | ļ        | $\Box$        |              | $\exists$                                        |                |                                                  | 二               | 二            |            |

| 1 1           | - 1                                       | _                   |                   |                          | 11           | 38       | +              | +              | -+       | +        | $\dashv$     | -+           |              |              | $\dashv$ | $\dashv$ |                | -                                                | -               | _        | $\vdash$       |                                                  | -        |               | $\dashv$     | 4                                                | _              | _                                                |                 |              | _          |

| 1 .:          | PURCHASE ORDER #                          | SIGNETICS DEVICE #  | TOTAL NUMBER OF P | PROGRAM TABLE # _<br>REV |              | 39       | I              | 丁              |          |          |              | +            | +            | $\dashv$     | $\dashv$ | -        | $\dashv$       |                                                  |                 | $\dashv$ | -              | $\dashv$                                         | $\vdash$ |               | $\dashv$     | $\dashv$                                         | -              | -                                                | $\dashv$        | $\dashv$     |            |

| ₩             | Ö                                         | 5 5                 | Σ<br>Σ            | <u>.</u> ب               | ļΈ           | 40       | T              | $\perp$        | I        | 1        |              |              | $\exists$    | $\Box$       |          |          |                |                                                  |                 |          |                | $\exists$                                        | +        | $\dashv$      | $\dashv$     | $\dashv$                                         | -              | $\dashv$                                         | -               |              |            |

| CUSTOMER NAME | P.                                        | DE DE               | 5                 | TABLE                    | {            | 41       | +              | +              | +        | +        | -            |              | 4            | [            | _]       | $\dashv$ | $\Box$         | $\Box$                                           |                 |          |                |                                                  |          |               |              | $\Box$                                           |                |                                                  |                 |              |            |

| E             | SE                                        | ပ္ပ                 | 2                 | - C<br>≥                 | 'nͰ          | 43       | +              | +              | +        | ╅        | +            | $\dashv$     | -+           |              | -        | [        |                | 4                                                |                 |          |                | $\dashv$                                         | L        | $\downarrow$  | I            | $\bot$                                           | ユ              | <b>_</b> Ţ                                       | $\Box$          | $\Box$       |            |

| ا ق           | Ĭ                                         |                     | د<br>ب            | Α̈́                      |              | 44       | 丁              | _              | _        | 1        | $\top$       | +            | 1            | -            | $\dashv$ | $\dashv$ | -              | ᅥ                                                |                 |          | -+             | $\dashv$                                         | +        | +             | -+           | +                                                | -              |                                                  |                 |              |            |

| TSI           | Ę,                                        | 2 5                 | < :               | ဗ >                      | ! F          | 45       | T              | 工              | I        | $\perp$  | $\dashv$     | $\exists$    | $\exists$    | コ            |          |          |                |                                                  |                 |          |                | _{                                               | $\vdash$ | 1             | $\dashv$     | +                                                | 1              | +                                                | $\dashv$        | -            | $\dashv$   |

| ರ             | ٦ ;                                       | Š                   | ָ                 | P P                      | ' <b> </b> - | 46       | 4              | 4              | $\bot$   | 4        | _            | $\bot$       | $\downarrow$ | [            | $ \bot $ | $\Box$   | $\Box$         | $\Box$                                           | $\Box$          | $\Box$   | $\Box$         |                                                  |          | ·             |              |                                                  | _†             |                                                  | $\neg$          | $\dashv$     | $\neg$     |

| (1) Inpu      |                                           |                     |                   |                          |              | 47       |                |                | Ц.       | 丄        | 丄            |              |              |              |          |          |                |                                                  | $\perp$         |          | $\Box$         |                                                  |          | $\Box$        | T            | I                                                | T              | T                                                |                 | $\neg$       | $\neg$     |

(1) Input and Output fields of unused P-terms can be left blank. Unused inputs and outputs are FPLA terminals left floating

FIGURE 3.46

Program table for a PLA.

BOOLEAN ALGEBRA AND GATE NETWORKS

FIGURE 3.47

Pin-out for PLA. (Signetics Corp.)

3.42 with a different symbology. This symbology becomes very useful when there are many inputs and gates, however.

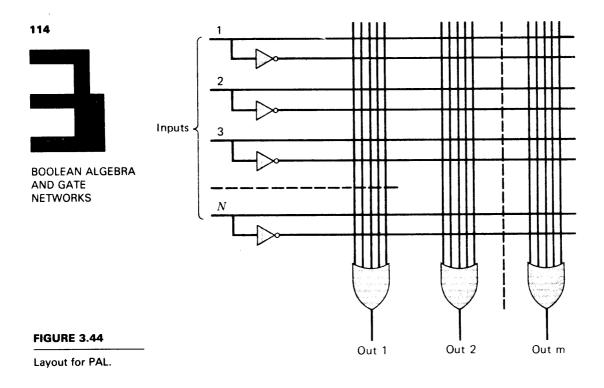

Figure 3.44 shows the layout for a version of the PLA which has become popular and which is called *programmable array logic*. The PALs are very similar to PLAs except that the OR gates are fixed and permanently connected to a set of AND gate output lines. As a result, AND gates cannot be shared, but the fixed OR gate connections lead to an ease of manufacture which has proved popular. Figure 3.45 shows a PAL design using the AND symbology (crosses) at intersections as in Fig. 3.43.

The current nomenclature calls the version of Fig. 3.44 in which the AND element connections are fused a PAL, but calls the version in which the manufacturer makes the connections *hard array logic* (HAL).

#### **EXAMPLE OF DESIGN USING A PLA**

**3.26** Since PLAs and PALs are widely used because of their economy and speed of operation, we examine the design of a small network employing a widely used table listing.

Program table for PLA design in Fig. 3.42.

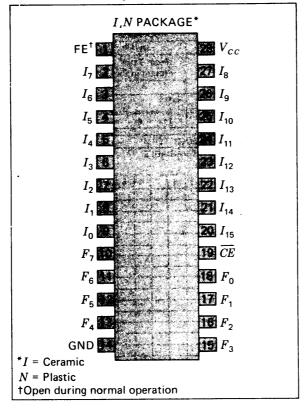

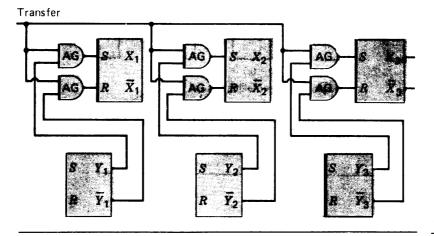

Figure 3.46 shows a program table for a PLA manufactured by Signetics. This PLA has 16 input variables and 8 outputs from OR gates. Also, 48 AND gates can be formed on the chip. This PLA is packaged in a 28-pin IC container, and the pin-out is shown in Fig. 3.47.

The table in Fig. 3.46 can be filled out to describe a particular gate network and then mailed to an IC manufacturer, who will then produce chips with a gate network corresponding to the table. Although a Signetics table is used here, the table is typical and other manufacturers provide the same service.

The table is filled out as follows:

First, the logic input variables are identified with the INPUT VARIABLE number 0 to 15 on the table. We fill out the table for Fig. 3.42 as a (small) example. To do this, we identify A with input 2, B with input 1, and C with input 0 on the program table. We now wish to form the product terms  $AB\overline{C}$ ,  $\overline{AB}$ , and AC. The rule is that if an input is not complemented (inverted), an H is written in the table; if the input is to be complemented, an L is written; and if the input is not used, a — is written. To form  $AB\overline{C}$ , then, we form a row in the table containing dashes everywhere except in INPUT VARIABLE columns 2, 1, and 0, and in these we write H, H, and L. This is shown in Fig. 3.48.

The OR gate inputs are written as follows:

If the AND term in a particular row is to be used in an OR output, an A (for

active) is written in the row; if not, a • is written. In Fig. 3.48, the OUTPUT FUNCTION line 0 in the table is associated with OUTPUT 1 in Fig. 3.42 and OUTPUT FUNCTION line 1 is associated with OUTPUT 2 in Fig. 3.42.

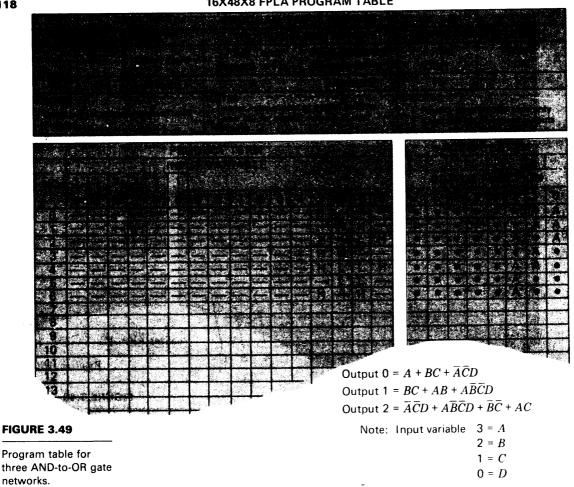

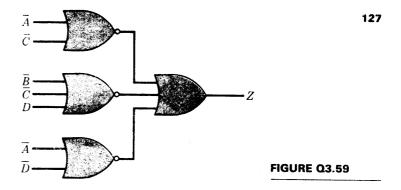

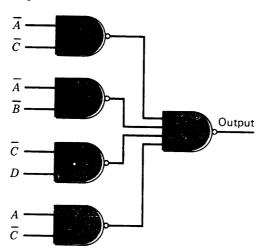

A final example is shown in Fig. 3.49. In this case, there are three output lines 0, 1, and 2. We associated A with INPUT VARIABLE 3 on the table, B with 2, C with i, and D with 0. The functions formed are

OUTPUT LINE

$$0 = A + BC + \overline{ACD}$$

OUTPUT LINE  $1 = AB + BC + A\overline{BCD}$

OUTPUT LINE  $2 = \overline{BC} + \overline{ACD} + A\overline{BCD} + AC$

Clearly PLAs provide a convenient way to fabricate IC chips with gate networks. The fact that field-programmable arrays with a given design can be made by blowing selected fuses and then the computer design can be tested by using these trial chips is very convenient. Later, for production runs, the chips made by a manufacturer from the table can be used.

This part of the IC business is sufficiently developed that PLA designs can be punched into cards and sent to a manufacturer, punched into tapes and sent to a manufacturer, and even sent over the telephone line from a terminal connected to a tape reader. (Manufacturers will provide a long-distance number you can call to phone in designs.)

#### **SUMMARY**

**3.27** This chapter presented the basic idea of a gate and showed how gates can be interconnected to form logic networks. The basic types of gates were introduced: AND, OR, NAND, and NOR gates and inverters.

The design of logic networks for computers is greatly facilitated by boolean algebra. This subject was introduced, and tables of combination, theorems of the algebra, and algebraic reduction of expressions were all explained.

The map method for simplifying boolean algebra expressions was presented. This makes it possible to minimize boolean expressions, thereby also simplifying the logic networks that realize these expressions. The various network forms such as AND-to-OR, NAND-to-NAND, OR-to-AND, NOR-to-NOR, NAND-to-AND, and NOR-to-OR networks were explained, and the design procedure for each was presented.

Gating networks can now be made with many gates in a single container by using LSI manufacturing techniques. The general layout for several such integrated circuits was presented, as was a special representation which is commonly used. This makes possible design of relatively large arrays of gates using PLAs, PALs, and HALs.

# QUESTIONS

**3.1** Prepare a truth table for the following boolean expressions:

(a)

$$XYZ + \overline{X}\overline{Y}\overline{Z}$$

(b)

$$ABC + A\overline{B}\overline{C} + \overline{A}\overline{B}\overline{C}$$

(c)

$$A(B\overline{C} + \overline{B}C)$$

$$(d) (A + B) (A + C) (\overline{A} + \overline{B})$$

**3.2** Prepare a table of combinations for the following boolean algebra expressions:

(a)

$$\overline{X}\overline{Y} + \overline{X}Y$$

(b)

$$XY\overline{Z} + \overline{X}\overline{Y}Z$$

$$(c) \ \overline{X}Y\overline{Z} + X\overline{Y}$$

$$(d) \ \overline{X}\overline{Y}\overline{Z} + X\overline{Y}\overline{Z} + \overline{X}Y\overline{Z}$$

(e)

$$\overline{X}\overline{Y} + \overline{Y}\overline{Z}$$

$$(f) \overline{A}B(\overline{A}\overline{B}\overline{C} + \overline{B}C)$$

**3.3** Prepare a truth table for the following boolean expressions:

(a)

$$A\overline{B} + \overline{A}B$$

(b)

$$A\overline{B} + B\overline{C}$$

(c)

$$A\overline{C} + AC$$

$$(d) \; \overline{ABC} + AB\overline{C} + \overline{ABC}$$

(e)

$$AB(A\overline{B}C + A\overline{B}\overline{C} + AB\overline{C})$$

**3.4** Prepare a table of combinations for the following boolean algebra expressions:

(a)

$$X(\overline{Y} + \overline{Z}) + X\overline{Y}$$

(b)

$$X\overline{Y}(Z + Y\overline{Z}) + \overline{Z}$$

(c)

$$[X(Y + \overline{Y}) + \overline{X}(\overline{Y} + Y)] \cdot \overline{Z}$$

$$(d) AB(\overline{A}B + \overline{A}\overline{B})$$

(e)

$$A[(\overline{B} + C) + \overline{C}]$$

$$(f) \ \overline{ABC} \ (\overline{ABC} + \overline{ABC})$$

**3.5** Prepare a table of combinations for the following boolean algebra expressions:

(a)

$$XY + \overline{X}\overline{Y}Z$$

(b)

$$ABC + A\overline{B} + \overline{AB}$$

(c)

$$ABC + \overline{AC}$$

QUESTIONS

BOOLEAN ALGEBRA AND GATE NETWORKS **3.6** Prepare a table of combinations for the following boolean algebra expressions:

(a)

$$A\overline{B}\overline{C} + \overline{A}B$$

(b)

$$\overline{ABC} + \overline{AC} + AB$$

(c)

$$XZ + X\overline{Y} + \overline{X}\overline{Z}$$

**3.7** Simplify the following expressions, and draw a block diagram of the circuit for each simplified expression, using AND and OR gates. Assume the inputs are from flip-flops.

(a)

$$A\overline{B}\overline{C} + \overline{A}\overline{B}\overline{C} + \overline{A}B\overline{C} + \overline{A}\overline{B}C$$

(b)

$$ABC + \overline{A}BC + A\overline{B}C + AB\overline{C} + A\overline{B}\overline{C} + \overline{A}B\overline{C} + \overline{A}B\overline{C}$$

(c)

$$A(A + B + C)(\overline{A} + B + C)(A + \overline{B} + C)(A + B + \overline{C})$$

(d)

$$(A + B + C) (A + \overline{B} + \overline{C}) (A + B + \overline{C}) (A + \overline{B} + C)$$

- **3.8** Simplify the expressions in Question 3.4 and draw block diagrams of gating networks for your simplified expressions, using AND gates, OR gates, and inverters.

- **3.9** Simplify the following expressions:

(a)

$$ABC (AB\overline{C} + A\overline{B}C + \overline{A}BC)$$

(b)

$$AB + A\overline{B} + \overline{A}C + \overline{A}\overline{C}$$

(c)

$$XY + XY\overline{Z} + XY\overline{Z} + XZY$$

$$(d) XY(\overline{X}Y\overline{Z} + X\overline{Y}\overline{Z} + \overline{X}\overline{Y}\overline{Z})$$

- **3.10** Simplify the expressions in Question 3.6 and draw block diagrams of gating networks for your simplified expressions, using AND gates, OR gates, and inverters.

- **3.11** Form the complements of the following expressions. For instance, the complement of (XY + XZ) is equal to  $(\overline{XY + XZ}) = (\overline{X} + \overline{Y})(\overline{X} + \overline{Z}) = \overline{X} + \overline{YZ}$ .

$$(a) (A + BC + AB)$$

(b)

$$(A + B) (B + C) (A + C)$$

(c)

$$AB + \overline{B}C + CD$$

(d)

$$AB(\overline{C}D + \overline{B}C)$$

(e)

$$A(B + C)(\overline{C} + \overline{D})$$

**3.12** Complement the following expressions (as in Question 3.11):

(a)

$$\overline{X}\overline{Y} + X\overline{Y}$$

(b)

$$X\overline{Y}Z + \overline{X}Y$$

(c)

$$\overline{X}(Y + \overline{Z})$$

(d)

$$X(Y\overline{Z} + \overline{Y}Z)$$

(e)

$$XY(\overline{Y}Z + X\overline{Z})$$

$$(f) XY + \overline{X}\overline{Y} (Y\overline{Z} + \overline{X}\overline{Y})$$

- **3.13** Prove the two basic De Morgan theorems, using the proof by perfect induction.

- **3.14** Prove the following rules using the proof by perfect induction:

$$(a) X\overline{Y} + XY = X$$

$$(b) X + \overline{X}Y = X + Y$$

**3.15** Convert the following expressions to sum-of-products form:

(a)

$$(A + B) (\overline{B} + C) (\overline{A} + C)$$

(b)

$$(\overline{A} + C) \cdot (\overline{A} + \overline{B} + \overline{C}) (A + \overline{B})$$

(c)

$$(A + C) (A\overline{B} + AC) (\overline{A}\overline{C} + \overline{B})$$

**3.16** Convert the following expressions to sum-of-products form:

(a)

$$(\overline{A} + \overline{B}) (\overline{C} + B)$$

(b)

$$\overline{A}B (\overline{B}C + \overline{B}C)$$

(c)

$$(\underline{A} + B\overline{C}) (\overline{A}\overline{B} + \overline{A}B)$$

$$(d) AB (A\overline{B}\overline{C} + \overline{A}C)$$

(e)

$$(\overline{A} + B) [A\overline{C} + (B + C)]$$

$$(f) (\overline{A} + C) (AB + \overline{AB} + AC)$$

- **3.18** Give a dual of the rule of  $X + \overline{X}Y = X + Y$ .

- **3.19** Multiply the following sum terms, forming a sum-of-products expression in each case. Simplify while multiplying when possible.

- (a) (A + C)(B + D)

- (b) (A + C + D) (B + D + C)

- (c) (AB + C + DC) (AB + BC + D)

- $(d) (A\overline{B} + \overline{A}B + A\overline{C}) (\overline{A}\overline{B} + A\overline{B} + A\overline{C})$

- **3.20** Convert the following expressions to product-of-sums form:

- (a)  $A + \overline{A}B + \overline{A}\overline{C}$

- (b)  $BC + \overline{A}B$

(c)  $A\overline{B}(\overline{B} + \overline{C})$

- $(d) \ \overline{AB} \ (\overline{BC} + \overline{BC})$

- (e)  $(A + \overline{B} + C) (AB + \overline{A}C)$

- $(f) (\overline{A} + \overline{B}) A\overline{B}C$

- **3.21** Write the boolean expression (in sum-of-products form) for a logic circuit that will have a 1 output when X = 0, Y = 0, Z = 1 and X = 1, Y = 1, Z = 0; and a 0 output for all other input states. Draw the block diagram for this circuit, assuming that the inputs are from flip-flops.

- **3.22** Convert the following to product-of-sums form

- (a)  $AB + \overline{A}(B + \overline{C}) (D + \overline{B})$

- (b)  $(B + C) [(\overline{B} + \overline{C}) (A + \overline{C}) (B + C)]$

- 3.23 Convert the following to product-of-sums form

- (a)  $AB\overline{C} + A\overline{B}C + \overline{A}BC$

- (b)  $ABC + \overline{BC} (A + CD) (B + C)$

- **3.24** Prove the following theorem, using the rules in Table 3.10:

$$(X + Y)(X + \overline{Y}) = X$$

- **3.25** Write the boolean expression (in sum-of-products form) for a logic network that will have a 1 output when X = 1, Y = 0, Z = 0; X = 1, Y = 1, Z = 0; X = 1, Y = 1, Z = 0; and X = 1, Y = 1, Z = 1. The circuit will have a 0 output for all other sets of input values. Simplify the expression derived and draw a block diagram for the simplified expression.

- **3.26** Derive the boolean algebra expression for a gating network that will have outputs 0 only when X = 1, Y = 1, Z = 1; X = 0, Y = 0, Z = 0; X = 1, Y = 0, Z = 0. The outputs are to be 1 for all other cases.

- **3.27** Prove rule 18 in Table 3.10, using the proof by perfect induction.

- **3.28** Develop sum-of-products and product-of-sums expressions for  $F_1$ ,  $F_2$ , and  $F_3$  in Table 3.27.

- **3.29** Develop both the sum-of-products and the product-of-sums expressions that describe Table 3.28. Then simplify both expressions. Draw a block diagram for logical circuitry that corresponds to the simplified expressions, using only NAND gates for the sum-of-products and NOR gates for product-of-sums expression.

QUESTIONS

BOOLEAN ALGEBRA AND GATE NETWORKS

|      | INPUTS |    | -              | OUTPUTS        |                |  |

|------|--------|----|----------------|----------------|----------------|--|

| X    | Y      | Z  | F <sub>1</sub> | F <sub>2</sub> | F <sub>3</sub> |  |

| A .v | 0      | O. | n .            | 0.0            | 1.3            |  |

| )    | Ŏ      | i  | Õ              | Î              |                |  |

| )    |        | 0  | 1 .            | 1              | 1              |  |

|      | Ó      | Ò  |                | 0,             | Ö              |  |

| •    |        |    |                |                |                |  |

|             | INPUTS |   | OUTPUT        |

|-------------|--------|---|---------------|

| X           | Y      | Z | A             |

| 0           | 0      | 0 | 0.4           |

| 0           | 0      | • | 1             |

| U           | •      | 1 | . 22 . 1<br>O |

| 0           |        |   |               |

| 0<br>1      | 0      | 0 | 0             |

| 0<br>1<br>1 | 0      | 0 | 0             |

- **3.30** Draw block diagrams for the  $F_1$ ,  $F_2$ , and  $F_3$  in Question 3.28, using only NAND gates.

- **3.31** Write the boolean algebra expressions for Tables 3.29 to 3.31, showing expressions in sum-of-products form. Then simplify the expressions and draw a block diagram of the circuit corresponding to each expression.

- **3.32** Draw block diagrams for the  $F_1$ ,  $F_2$ , and  $F_3$  in Question 3.28, using only NOR gates.

- **3.33** Draw block diagrams for  $F_1$ ,  $F_2$ , and  $F_3$  in Question 3.28, using OR-to-NAND networks.

- **3.34** Draw block diagrams for  $F_1$ ,  $F_2$ , and  $F_3$  in Question 3.28, using AND-to-NOR gate networks.

- **3.35** Draw Karnaugh maps for the expressions in Question 3.2.

- **3.36** Draw Karnaugh maps for the expressions in Question 3.3.

- **3.37** For a four-variable map in W, X, Y, and Z draw the subcubes for:

(a)  $WX\overline{Y}$  (b) WX (c)  $XY\overline{Z}$  (d) Y

- **3.38** For a four-variable map in W, X, Y, and Z draw the subcubes for:

(a)  $\overline{W}X\overline{Y}\overline{Z}$  (b)  $W\overline{Z}$  (c)  $\overline{W}Z$  (d)  $\overline{Y}$

| TAE | BLE 3.29 |                |              |

|-----|----------|----------------|--------------|

|     | INPUTS   |                | OUTPUT       |

| A   | В        | С              | Z            |

| 0   | 4.70     | W. <b>0</b> /. | <b>y</b> y   |

| 0   |          | , å · · ·      |              |

| 0   | 00       | No. 20         | 0<br>(1)     |

| 1   | . 0      | n sales.       | 1            |

| i i | i        | 1              | The board of |

- **3.39** Draw maps of the expressions in Question 3.40; then draw the subcubes for the shortened terms you found.

- **3.40** Apply the rule  $AY + A\overline{Y} = A$ , where possible, to the following expressions:

(a)

$$X\overline{Y} + \overline{X}\overline{Y}$$

$$(b) \ \overline{A}\overline{B}\overline{C} + A\overline{B}\overline{C}$$

(c)

$$A\overline{B}C + ABC$$

$$(d) ABC + A\overline{B}\overline{C} + A\overline{B}C + AB\overline{C}$$

(e)

$$ABC + \overline{A}\overline{B}\overline{C} + A\overline{B}C$$

$$(f) ABC + \overline{A}BC + \overline{A}\overline{B}\overline{C}$$

Note: There is a technique for writing minterms that is widely used. It consists in writing the letter m (to represent minterm) along with the value of the binary number given by the row of the table and combinations in which the minterm lies. For instance, in the variables X, Y, Z we have the unfinished table of combinations given in Table 3.32.

| TAB | LE 3.30 |     |                                         |

|-----|---------|-----|-----------------------------------------|

|     | INPUTS  |     | OUTPUT                                  |

| A   | В       | С   | Z                                       |

| 0   | 0       | 0   |                                         |

| ŏ   | Í       | Ó   | 1 3 C 3 C 3 C 3 C 3 C 3 C 3 C 3 C 3 C 3 |

| 1   |         | . 0 |                                         |

| 1   | 1       | 0   | 0                                       |

| 1   | 1       | 1   |                                         |

| TAB     | LE 3.31     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|         | INPUTS      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OUTPUT         |

| X       | Y           | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P              |

|         | 40          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Ď       | 0.0         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1. 2           |